Du point de vue d’un passionné d’informatique x86 traditionnel ou d’un professionnel, les mainframes sont des bêtes étranges et archaïques. Ils sont physiquement énormes, énergivores et chers par rapport aux équipements de centre de données plus traditionnels, offrant généralement moins de calcul par rack à un coût plus élevé.

Cela soulève la question « Pourquoi continuer à utiliser des ordinateurs centraux, alors ? » Une fois que vous avez brandi à la main les réponses cyniques qui se résument à « parce que c’est ainsi que nous l’avons toujours fait », les réponses pratiques se résument en grande partie à la fiabilité et à la cohérence. Comme le souligne Ian Cutress d’AnandTech dans une spéculation pièce concentré sur le cache redessiné de Telum, « les temps d’arrêt de ces [IBM Z] systèmes est mesurée en millisecondes par an. » (Si c’est vrai, c’est au moins Sept neuf.)

le propre d’IBM annonce de Telum indique à quel point les priorités de l’ordinateur central et de l’informatique de base sont différentes. Il décrit avec désinvolture l’interface mémoire de Telum comme « capable de tolérer des pannes complètes de canaux ou de modules DIMM, et conçue pour récupérer les données de manière transparente sans impact sur le temps de réponse ».

Lorsque vous extrayez une barrette DIMM d’un serveur x86 en cours d’exécution, ce serveur ne « récupère pas les données de manière transparente » – il se bloque simplement.

Architecture IBM série Z

Telum est conçu pour être une sorte de puce unique pour tous les mainframes, remplaçant une configuration beaucoup plus hétérogène dans les mainframes IBM antérieurs.

Le processeur IBM z15 14 nm que Telum remplace comprend cinq processeurs au total : deux paires de processeurs de calcul à 12 cœurs et un contrôleur système. Chaque processeur de calcul héberge 256 Mo de cache L3 partagé entre ses 12 cœurs, tandis que le contrôleur système héberge un énorme 960 Mo de cache L4 partagé entre les quatre processeurs de calcul.

Cinq de ces processeurs z15, chacun composé de quatre processeurs de calcul et d’un contrôleur système, constituent un « tiroir ». Quatre tiroirs sont réunis dans un seul châssis principal alimenté par le z15.

Bien que le concept de plusieurs processeurs dans un tiroir et de plusieurs tiroirs dans un système demeure, l’architecture à l’intérieur de Telum elle-même est radicalement différente et considérablement simplifiée.

Architecture en télum

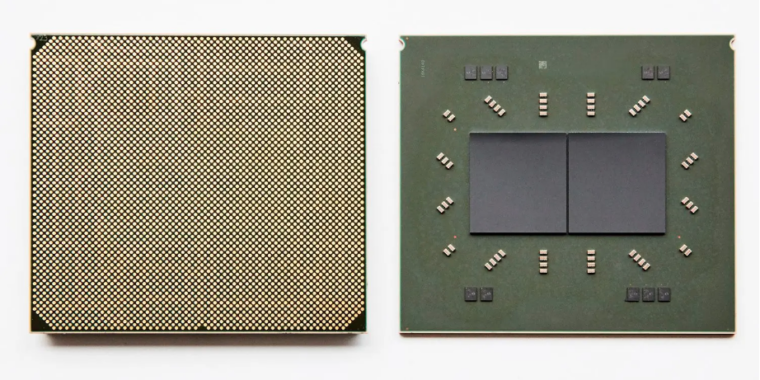

Telum est un peu plus simple à première vue que le z15 : c’est un processeur à huit cœurs construit sur le processus 7 nm de Samsung, avec deux processeurs combinés sur chaque boîtier (similaire à l’approche chiplet d’AMD pour Ryzen). Il n’y a pas de processeur de contrôleur système distinct—tous les processeurs de Telum sont identiques.

À partir de là, quatre packages de processeurs Telum se combinent pour former un « tiroir » à quatre sockets, et quatre de ces tiroirs vont dans un seul système central. Cela fournit 256 cœurs au total sur 32 processeurs. Chaque noyau fonctionne à un base fréquence d’horloge supérieure à 5 GHz, offrant une latence plus prévisible et cohérente pour les transactions en temps réel qu’une base inférieure avec un taux turbo plus élevé.

Poches pleines de cache

Supprimer le processeur système central sur chaque package signifiait également reconcevoir le cache de Telum – l’énorme cache L4 de 960 Mo a disparu, ainsi que le cache L3 partagé par puce. Dans Telum, chaque cœur individuel dispose d’un cache L2 privé de 32 Mo, et c’est tout. Il n’y a pas du tout de cache matériel L3 ou L4.

C’est là que les choses deviennent profondément étranges – alors que le cache L2 de 32 Mio de chaque cœur Telum est techniquement privé, c’est vraiment seulement virtuellement privé. Lorsqu’une ligne du cache L2 d’un cœur est expulsée, le processeur recherche un espace vide dans le L2 des autres cœurs. S’il en trouve, la ligne de cache L2 expulsée du noyau X est étiqueté comme une ligne de cache L3 et stocké dans le noyau oui‘s L2.

OK, nous avons donc un cache L3 virtuel partagé jusqu’à 256 Mo sur chaque processeur Telum, composé du cache L2 « privé » de 32 Mo sur chacun de ses huit cœurs. À partir de là, les choses vont encore plus loin : 256 Mo de « L3 virtuel » partagé sur chaque processeur peuvent, à leur tour, être utilisés comme « L4 virtuel » partagé entre tous les processeurs d’un système.

Le « L4 virtuel » de Telum fonctionne en grande partie de la même manière que son « L3 virtuel » le faisait en premier lieu : les lignes de cache L3 expulsées d’un processeur recherchent une maison sur un processeur différent. Si un autre processeur du même système Telum a de l’espace libre, la ligne de cache L3 expulsée est réétiquetée en tant que L4 et vit dans le L3 virtuel sur l’autre processeur (qui est composé des L2 « privés » de ses huit cœurs).

Ian Cutress d’AnandTech va plus loin détail sur les mécanismes de cache de Telum. Il finit par les résumer en répondant « Comment est-ce possible ? avec une simple « magie ».

Accélération de l’inférence de l’IA

Christian Jacobi d’IBM décrit brièvement l’accélération de l’IA de Telum dans ce clip de deux minutes.

Telum présente également un accélérateur d’inférence sur puce 6TFLOPS. Il est destiné à être utilisé, entre autres, pour la détection de fraude en temps réel pendant transactions financières (par opposition à peu de temps après la transaction).

Dans la quête de performances maximales et d’une latence minimale, IBM enfile plusieurs aiguilles. Le nouvel accélérateur d’inférence est placé sur la puce, ce qui permet des interconnexions à latence plus faible entre l’accélérateur et les cœurs du processeur, mais c’est ne pas intégré dans les cœurs eux-mêmes, un jeu d’instructions AVX-512 d’Intel.

Le problème avec l’accélération d’inférence dans le cœur comme celle d’Intel est qu’elle limite généralement la puissance de traitement de l’IA disponible pour un seul cœur. Un cœur Xeon exécutant une instruction AVX-512 ne dispose que du matériel à l’intérieur de son propre cœur, ce qui signifie que les tâches d’inférence plus importantes doivent être réparties entre plusieurs cœurs Xeon pour extraire toutes les performances disponibles.

L’accélérateur de Telum est sur matrice mais hors cœur. Cela permet à un seul cœur d’exécuter des charges de travail d’inférence avec la puissance du tout accélérateur sur matrice, pas seulement la partie intégrée en elle-même.

Image de la liste par IBM